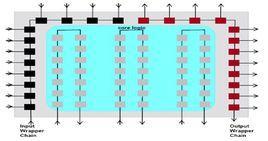

APT是一个程序开发语言,Automatic Test Pattern Generation(ATPG)自动测试向量生成是在半导体电器测试中使用的测试图形向量由程序自动生成的过程。测试向量按顺序地加载到器件的输入脚上,输出的信号被收集并与预算好的测试向量相比较从而判断测试的结果。ATPG有效性是衡量测试错误覆盖率的重要指标。

精选百科

本文由作者推荐

ATPG相关的文章

小编整理:欧麦尔二世是阿拉伯帝国伍麦叶王朝的第八任哈里发,他在位时间为717年至720年。欧麦尔二世是阿卜杜勒·阿齐兹的儿子,他的全名为欧麦尔·本·阿卜杜勒·阿齐兹·本·麦尔旺·本·哈凯姆。欧麦尔二世生于埃及的赫勒万,他在其父的熏陶下自幼能背诵《古兰经》,并初

大西洋(Atlantic Ocean),是世界第二大洋,占地球表面积的近20%,原面积9165.5万平方千米,在南冰洋成立后,面积调整为7676.2万平方千米,平均深度3627米,最深处波多黎各海沟深达9219米。

甜瓜(学名:Cucumis melo L.)是葫芦科(Cucurbitaceae)黄瓜属(Cucumis)植物,别名白兰瓜、哈密瓜、香瓜。甜瓜原产于印度和非洲国家,后广泛引种于世界温带至热带地区,中国各地广泛栽培。甜瓜喜光照,喜温耐热,常生长在土层深厚、通透性好、不易积水的沙土中。

西奈半岛是连接非洲及亚洲的三角形半岛,面积61000平方公里(23500平方英里)。西滨苏伊士湾和苏伊士运河,东接亚喀巴湾和内盖夫沙漠,北临地中海,南濒红海。东西最宽约210公里(130英里)、南北最长约385公里(240英里)。半岛上广大的干燥地区称为西奈沙漠,西与埃及的东部沙漠间隔着苏伊士湾及运

亚历山大大帝本词条是多义词,共7个义项马其顿国王西方四大军事统帅之首亚历山大大帝(希腊文:Αλέξανδρος,英文:Alexander the Great;前356年-前323年6月13日),即亚历山大三世,马其顿王国(亚历山大帝国)国王,生于古马其顿王国首都佩拉,马其顿国王腓力二世之子,世界古代史上著名的军事家和政治家。是欧洲历史上最伟大的四大军事统帅之首。曾师从古希腊著名学者亚里士多德,16

尚可名片

这家伙太懒了,什么都没写!

作者