亚微米和深亚微米MOS器件

通常把0.8-0.35um称为亚微米,0.25um及其以下称为深亚微米,0.05um及其以下称为纳米级。深亚微米制造的关键技术主要包括紫外光刻技术、等离子体刻蚀技术、离子注入技术、同互连技术等。目前,国际上集成电路的主流生产工艺技术为0.18-0.25um,预计2006年主流加工技术将提高到0.lum,2012年将达到0.05um,进入纳米级。深亚微米集成电路要求硅单晶材料向大直径和无(少)缺陷方向发展。对于已开始应用的300毫米硅单晶而言,磁场拉晶、计算机模拟、线切割、双面抛光等工艺成为大直径硅单晶研制的重要特征;利用晶体生长速率和固液界面的温度梯度的设计,硅单晶中的自间隙硅原子、空位以及相关的微缺陷可以被控制;通过快速热处理,引入和控制空位,进而控制氧沉淀的新型内吸杂技术,可以制备高质量的表面清洁区;利用氮杂质掺杂,可以抑制硅单晶中VOID缺陷和增加硅片的机械强度. 超深亚微米集成电路和微机电系统的膜/基和多层异质膜结构及内导线结构所用材料尺度逐渐由微米级减小到亚微米甚至纳米级,即处于传统宏观与微观范畴之间的介观材料领域,其服役可靠性问题具有持久的挑战性。材料性能的尺度效应,表面和界面效应及异质约束效应等愈加凸现,成为影响其可靠性的决定性因素之一。因此,材料介观性能,特别是服役性能的正确表征成为关系到提高微器件设计制造水平和服役可靠性而亟待解决的关键问题.

深亚微米电路设计对设计流程的影响

当前硅集成电路工业已进入0.5μm特征尺寸产品的大生产阶段,0.35μm工艺也已投入试生产。1994年半导体工业协会公布了1995—2010年15年间集成电路技术发展的预测。21世纪头10年将面临如何进行0.1μm级电路的设计和制造问题。生产工艺从微米、亚微米发展到深亚微米,这一变化对集成电路设计及其设计方法学 提出了新的问题和挑战。首先要解决的是建立起精确的深亚微米器件模型、时序模型和互连模型。在深亚微米级电路设计中的一个突出矛盾是时序问题。到了深亚微米水平,互连线的延迟将超过门延迟;而且由于集成电路工作频率的提高,允许的时序容差变小,传输延迟的影响加大,这对电路设计带来了难度。在微米级电路设计时,习惯上把设计分成前后两个阶段。前一阶段统称逻辑设计,这时进行系统和功能设计以及结构和电路设计;后一阶段称为版图设计,主要进行布局、布线以及物理验证和掩膜生成。两者之间的沟通主要通过网表和单元库。前端设计完成后将网表传递给版图设计人员,一般讲只要布线能够布通,时序要求就能够满足。到了深亚微米阶段,情况就不同了,如果前端设计中不能充分考虑后端设计即物理实现时的各种问题,特别是物理实现后引起的时序问题,那就会造成逻辑设计与物理设计的结果不一致。在逻辑设计中经过仿真分析在功能和时序上都正确的网表,经过实际的布局布线后,由于互连延迟取决于具体的布线且在整个芯片延迟中起主要作用,更由于逻辑设计时所用的互连延迟模型与实际的互连延迟特性不一致,因而最终的时序会变得不再满足设计要求。这就需要反过来修改逻辑设计,重新进行仿真分析。如果逻辑设计仍不能取得精确的、实际的互连延迟数据,那么即使经过修改仍不能得到合乎要求的物理设计。如此下去,就会导致逻辑设计与物理设计的设计循环“不收敛”,使设计周期大大加长。

深亚微米集成电路中的ESD保护问题

随着集成电路制造工艺水平进入集成电路线宽的深亚微米时代,集成电路中的MOS元件都采用LDD结构(Lightly Doped Drain),并且硅化物工艺已广泛应用于MOS元件的扩散层上,同时为了降低栅极多晶的扩散串联电阻,采用了多晶化合物的制造工艺。此外随着集成电路元件的缩小,MOS元件的栅极氧化层厚度越来越薄,这些制造工艺的改进可大幅度提高集成电路内部的运算速度,并可提高电路的集成度。但是这些工艺的改进带来了一个很大的弊端,即深亚微米集成电路更容易遭受到静电冲击而失效,从而造成产品的可靠性下降。

深亚微米集成电路中的ESD问题

(1)工艺引入问题

LDD结构是用来降低MOS管源端和漏端在沟道的电场分布,以克服热载流子效应(Hot carriereffect)所造成的I-V特性因长时间作用而漂移的问题。但是LDD结构在导电沟道两段的深度只有20nm,这等于在源极和漏极的两端形成了两个"尖端","尖端放电"现象便容易发生在LDD结构上,从而造成这种结构的抗静电能力较低。当这种LDD元件应用于输出级电路时,NMOS元件很容易被ESD所破坏。即使元件具有很大的宽长比,其抗静电能力常低于1 000V。此外,金属硅化物工艺在深亚微米集成电路工艺中已被广泛采用,其目的是为了降低MOS元件在其源极和漏极的串联电阻。在不采用金属硅化物工艺的条件下,N+扩散区的阻值约为30~40Ω/□,但在金属硅化物工艺条件下其阻值降低到1~3Ω/□,由于扩散层的方块电阻大幅降低,使得MOS元件的速度可以大幅度提高。但当金属硅化物扩区的MOS元件被用来做输出级的元件时,由于其源漏电阻都很小,ESD电流便很容易经由PAD传导到MOS元件的LDD结构,极容易因LDD"尖端放电"而把MOS元件破坏掉,故在深亚微米集成电路中,MOS元件的ESD能力大幅度下滑,制造大尺寸的输出级元件也无法有效地提升其抗静电能力。

(2)传统电路ESD保护设计及其缺陷

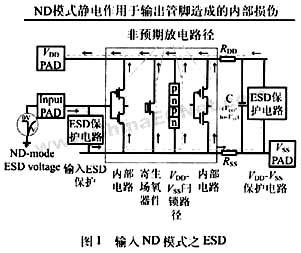

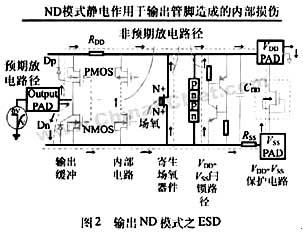

在传统ESD设计上,静电保护元件一般只做在I/O与VSS之间,在PAD与VDD、VSS和VDD之间没有静电保护元件,在这种静电保护设计之下,集成电路内部常出现异常损伤问题。在对地正脉冲(PS)、对地负脉冲(NS)、对电源正脉冲(PD)、对电源负脉冲(ND)四种放电模式中,在图1中ND模式的静电放电负电压出现在输入与VDD之间,VDD在此模式下接地,此负的ESD电压会首先经由输入保护电路传递到VSS电源线上,因VSS电源线在此模式下是浮接的,故加在输入上的负电压会被传递到VSS上,在此模式下,原本电压降在输入与VDD之间的负ESD电压,转变成降在VDD与VSS之间,如果该ESD电压未能有效且快速的被VDD到VSS的静电放电保护电路旁路掉,ESD电压会由VDD与VSS电源线而进入集成电路内部。由于内部元件具有最小的尺寸与间距以节省面积,因而特别容易因ESD而失效,而由于电路内的VDD与VSS布线较长,容易造成一些离散的电阻(Rdd与RSS)与扩散电容(C),这些离散电阻和电容的分布如图1所示,造成该模式下的NDESD不易被旁路掉。

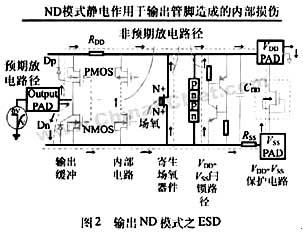

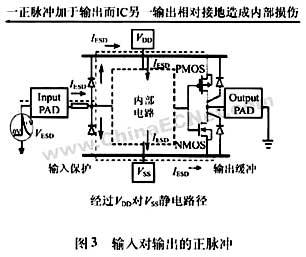

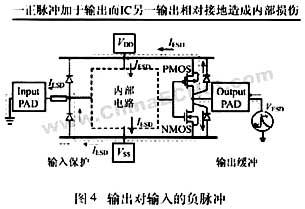

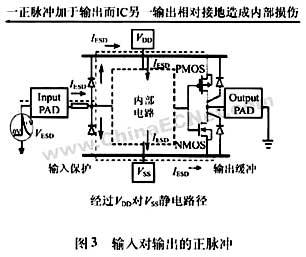

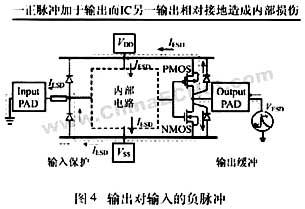

图2所示为一ND模式的。ESD负电压出现在输出PAD上造成内部损伤的示意图。当一ND模式的ESD负电压出现在输出PAD,在VDD接地输出缓冲级内的PMOS元件会因电压过高而击穿导通来旁路ESD静电电流。但在PMOS元件击穿导通之前,该ND模式的ESD负电压会先经由输出缓冲级的NMOS元件传递到浮接的VSS电源线,因此原本出现在输出与VDD之间的ESD负电压会转而降在VDD与VSS之间导致电路内部的ESD损伤。图3为一正脉冲加于输入而IC另一输出相对接地,图4为一负脉冲加于输出对IC另一输入相对接地的电流流向示意图。图3中可能造成输入脚的ESD保护二极管Dnl崩溃来旁通ESD电流到浮接的VSS上,该电流再由输出脚的NMOS寄生二极管Dn2流出。但是在:Dn2击穿前,该ESD电流会先经由该输入脚的另一ESD保护二极管Dp2而对浮接VDD充电,而浮接的VSS也会因输出脚接地而被Dn2偏压在接近地的电位,因此,发生在已输入脚相对另一输出脚的ESD电压会转变成在VDD与VSS之间的过电电压,该电流会随着VDD与VSS之间而进入集成电路内部而造成电路内部损伤,但输入/输出的ESD保护电路仍能完好无缺,ESD造成的内部损伤可能会使得VDD对VSS的漏电增加,也可能烧毁集成电路内部的元件而使得电路丧失部分的功能,这内部损伤要有功能测试才能找到损伤位置,而ESD造成的内部破坏的位置是一随机现象,很难防范。图4在负电压下,浮接的VSS会因寄生在输出NMOS的二极管Dn2而被偏压到接近负ESD电压,而浮接的VDD电源则被输入到二极管Dpl偏压在已接近地的电位。因此,原本出现住输出对输人的负电压会变为VSS到VDD电源线之间的ESD电压,而电压会经VDD与VSS而进入集成电路内部,从而造成电路损伤。这种损伤方式比上面输入/输出对VDD和VSS情况更易发生,且不易有输入到输出的漏电发现,因此常在ESD测试仪上被误判为正常元件。

为了箝制过高的ESD电压跨在VDD与VSS电源线之间,须在二者之间设计保护电路。一大尺寸栅极接地的NMOS组件连接于IC的VDD与VSS电源线之间,被用来做VDD到VSS静电放电防护电路。若有ESD电压出现在VDD与VSS电源线之间,该NMOS组件将会崩溃导通来旁通该ESD的放电电流。但是,即使有该NMOS组件做.ESD防护组件来旁通ESD放电电流,IC的内部电路依然会出现ESD损伤的问题。因为,该NMOS组件除了提供ESD防护来保护IC内部电路之外,它也要能够保护自己不被ESD电流所破坏,以免因其被ESD损毁而导致该IC无法正常使用。为了保护NMOS组件不被ESD电流所破坏,该NMOS组件通常在布局上便无法使用最小的布局间距。然而,IC的内部电路经常是使用最小的布局间距,这导致了一个问题,就是内部电路组件因具有最小的布局间距,会先崩溃导通,而ESD保护用电路中的NMOS元件因具有较大的布局间距,反而较慢崩溃导通,这使得栅极接地的NMOS组件不能够有效地保护IC的内部电路。

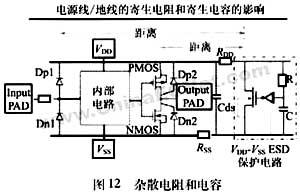

(3)电源/地线上杂散电容/电阻效应

虽然深亚微米集成电路中的改良设计能够充份保护IC内部电路,避免异常的ESD损伤。但是在电源/地线上的寄生电阻与电容效应会降低改良电路的保护效果。因为ESD放电现象在很短的时间内(约l00ns)便会出现高达数安培的放电电流,如果该改进ESD箝制电路的位置距离ESD的输入或输出脚位太远,则可能会发生时间上来不及启动保护电路的现象。在深亚微米VLSI中,芯片的尺寸越来越大,相对地环绕整个芯片的VDD与VSS电源线更长,其所相对产生的杂散电容/电阻效应也会增加,这反而降低了ESD箝制电路的防护效果。

深亚微米集成电路ESD保护改进技术

(1)工艺上的改进

为了提高深亚微米集成电路的抗静电能力,目前有ESD注入、金属硅化物扩散层分隔和N阱电阻三种ESD保护改进工艺应用于深亚微米集成电路制造过程中。

为了克服因LDD结构所造成电路抗静电能力的下降.便出现了ESD注入工艺。其原理是在同一电路上做出两种不同的NMOS元件,一种是给内部电路单元使用,具有LDD结构的NMOS元件;另一种是给I/O使用,不具有LDD结构的NMOS元件。但利用ESD注入过程做的元件拥有较深的结面深度,故会有较严重的横向扩散作用,所以利用ESD注入过程所作的NMOS元件不能用太短的沟道长度。此外利用ESD注入工艺做的NMOS元件与LDD结构的NMOS元件不同,故需要额外的处理及设计来提取这种ESD注入工艺NMOS元件的SPICE参数,以利于电路模拟与设计工作的进行。另外一种ESD注人工艺是将一掺杂浓度较高的硼注人到接触孔正下方的N型扩区和P型衬底之间,以降低该结面的击穿电压。因为该结面具有较低的崩溃电压,当静电放电出现在NMOS元件的漏极时,静电放电电流便会先由该低击穿电压的结面放电。利用这种工艺过程,NMOS元件仍可使用LDD结构且具有较短沟道长度,且该NMOS元件的SPICE参数跟其他NMOS元件相同,除了该结面击穿电压之外,不必另外抽取这种ESD注入的NMOS的SPICE参数。

为了提高输出级的ESD能力,在工艺上还开发出了金属硅化物扩散层分隔工艺。其原理是把输出级用的NMOS元件中的金属硅化物去除,使其源极和漏极的方块电阻值回到30~40Ω/□,从而提高MOS元件的抗静电能力。

在深亚微米集成电路制造工艺上还采用N阱电阻的方法来提高电路的抗静电能力。原理是将输出NMOS管漏极的N+扩区断开,位于中间的N+扩区被连出当漏极,而断开区域(场氧区域)利用N阱把中间的N+扩区连接到MOS管的漏极N+扩区上。此处N阱的作用用来限制ESD放电的瞬间峰值电流。另外在接触孔下有N阱结构,可防止ESD电流造成漏极与P型衬底间短路。利用工艺上场氧区域的间距大小即可做出不同大小的N阱电阻,这种电阻会影响到输出级的能力,但只要加大输出级的元件宽度即可使其恢复到正常的推动能力。

(2)静电保护元件上的改进

集成电路在生产工艺上的改进必将会增加电路制造的复杂程度和成本,如果能开发出不须改变工艺的静电保护元件将具有更大的意义。低电压触发可控硅(Low Voltage Triggering SCR,简称LVTSCR)便是在单位面积下具有较高抗静电能力的保护元件。利用这种元件,CMOS集成电路的抗静电能力能够只占用很小面积便可达到较高的抗静电能力。

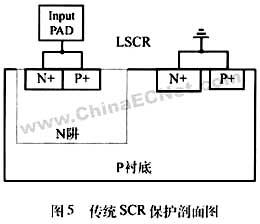

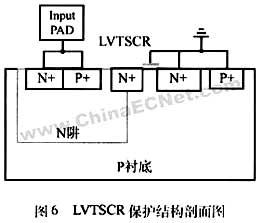

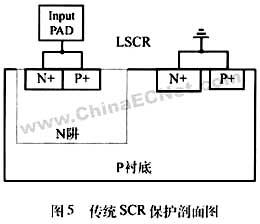

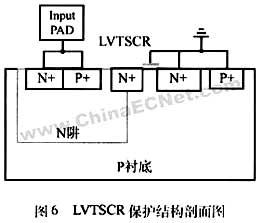

SCR元件的基本结构如图5所示。这种保护元件能在最小的布局面积下提供最高的ESD保护能力。但若只是简单的四层结构,则此SCR元件起始导通电压等于CMOS工艺下N阱和P衬底结面的击穿电压。由于N阱掺杂浓度较低,故其结面击穿电压在30~50V之间。具有如此高的结面击穿电压,使得SCR元件在ESD保护上需要加上第二级保护电路。第二级保护电路的目的在于提供较低电压时的ESD保护能力。但第二级保护电路会占用额外的布局面积,使得在PAD附近的版图结构变得复杂。常用的第二级保护结构为一个短沟道的NMOS元件,结构如图6所示。此改进SCR的起始导通电压等于短沟道NMOS元件的击穿电压,大约在10~15V左右。其原理是利用内嵌的短沟道NMOS元件发生击穿时,引发电流自N阱流向P衬底,因而触发了SCR元件的导通。为了防止该保护元件在正常工作情况下不会被导通,其内含的短沟道NMOS的栅极连到地上,以保持该NMOS元件在电路正常工作时是关闭的。这种LVTSCR元件的ESD能力得以大幅度提高且不需要额外的工艺处理步骤,但其缺点是不易设计,需要相当的经验才能够充分使得原本是缺点的寄生元件变为ESD保护的元件。

在进行集成电路I/O端口对电源和地的静电放电组合实验中,在对地正脉冲(PS)、对地负脉冲(NS)、对电源正脉冲(PD)、对电源负脉冲(ND)四种放电模式中,PS和ND模式最易导致集成电路损伤。在以前的设计中,LVTSCR只被安排在PAD地的放电路径上,故在先前的设计中仍欠缺对电源负脉冲保护的设计。

(3)电路改进方法

电路改进来提升集成电路的抗静电能力,主要是利用ESD放电的瞬间电压快速变化的特性,由电容耦合作用来使得ESD保护元件达到更好的保护作用。

1)栅极耦合技术

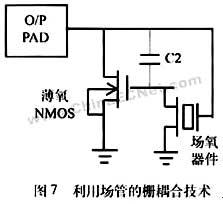

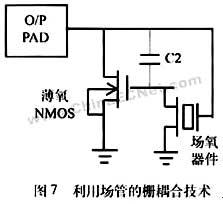

在深亚微米集成电路工艺中,元件的ESD能力下降,为了提升集成电路的抗静电能力,在输入/输出PAD处的ESD保护元件或输出级元件都会做得比较大,经常布图为插指状。但在ESD时,由于相对位置和布线方向不同并非所有插指能同时导通。所以即使元件尺寸已做得很大也未必能如预期地提升ESD保护能力。为了克服上述问题图7、图8给出了利用电容耦合作用来使大尺寸集成电路的每一插指都能均匀导通的设计。图7为利用NMOS的扩散栅漏电容作耦合无件,另外一场氧元件加强了耦合电容的作用,当有正的ESD电压时,瞬间电压变化会导致NMOS栅极电压跟着上升,由于电容耦合作用,因为NMOS栅极上有耦合的正电压,故大尺寸NMOS元件的各个插指会一起进入击穿区,因此其ESD防护能力便可充分发挥。

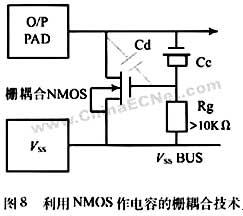

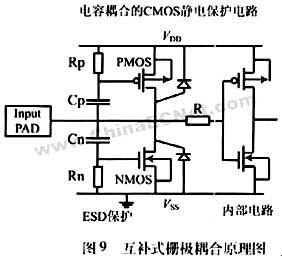

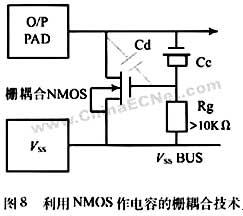

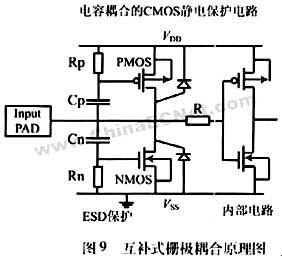

图8为电容耦合技术应用于输入级ESD保护的。种结构,栅耦合NMOS是ESD电流旁通用的元件,具有较大的尺寸。因应用于输入端,故其栅极须经电阻接地,该结构在正常工作时是常闭的。另有NMOS连结成电容,此NMOS是用来加强电容耦合作用。当有正的ESD电压作用在输入PAD上发生时,一部分正电压会经Cd与Cc的耦合作用到栅耦合NMOS的栅极,此栅极电流会经Rg放电到地上,Rg的大小会影响到栅极电压的维持时间,GCNMOS因而可以达到均匀导通的目的,以提升其抗静电能力。2)互补式栅极耦合技术

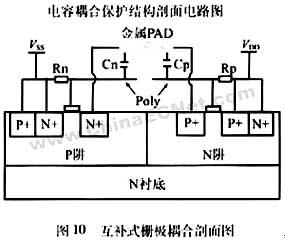

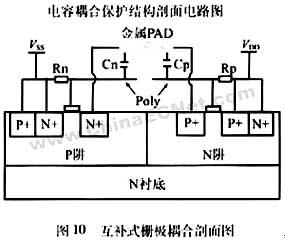

互补式栅极耦合技术是同时有对电源和地的栅极耦合NMOS元件。在任意I/O端口上的ESD放电有四种测试组合,所以ESD设计必须考虑这四种情况下的放电回路。选择合适的Cn(Cp)与Rn(Rp),能够提供有效的ESD保护而不影响电路的正常工作状态。图9和图10给出了此电路保护电路的原理图和剖面结构图,该耦合电容可以利用PAD与其下方的多晶层的寄生电容来实现,这样设计可以节省电路布局面积。

3)深亚微米集成电路的VDD对VSS防护技术

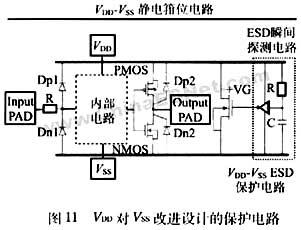

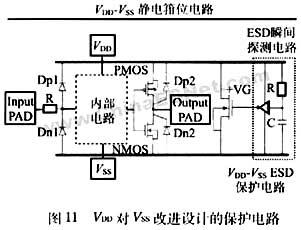

为提升该NMOS组件的ESD保护功效,图11为改良式的设计。在图中,一静电放电侦测电路被加入,用来控制该NMOS组件的栅极。当有ESD电压出现跨在VDD与VSS电源线上时,该静电放电侦测电路会送出一正电压把NMOS组件导通来旁通掉ESD放电电流。由于该NMOS元件是藉由其栅极控制而导通,而不是像栅极接地NMOS组件是靠崩溃才导通的,因此具有极低的导通电压。当内部电路组件尚未因ESD电压崩溃之前,该NMOS组件就早已导通来旁通ESD放电电流了。这导通的NMOS组件在VDD与VSS之间成一暂时性的低阻抗状态,因此跨在VDD与VSS之间的ESD电压能够很有效地被箝制住,不会再造成IC内部电路因ESD 而出现异常损坏的现象。利用此一改良式的ESD箝制电路,可以有效地防护脚对脚的ESD放电。当管脚对管脚ESD电压转变成跨在VDD与VSS电源线之间时,该RC控制的ESD侦测电路会因ESD的能量而偏压工作,并送出正电压到NMOS组件的栅极来导通该NMOS,ESD电流便经由这导通的NMOS组件而排放掉,因此IC的内部电路及寄生的SCR与BJT组件都不会因为ESD的过压而破坏。

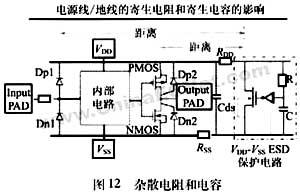

在深亚微米集成电路设计中,为了避免图12所示这杂散电容/电阻的影响,电源线的宽度/长度与ESD 箝制电路的摆放位置需要建立一套设计准则,以利IC设计上的参考。