ECL(Emitter Coupled Logic)即发射极耦合逻辑电路,也称电流开关型逻辑电路。它是利用运放原理通过晶体管发射极耦合实现的门电路。

精选百科

本文由作者推荐

ECL相关的文章

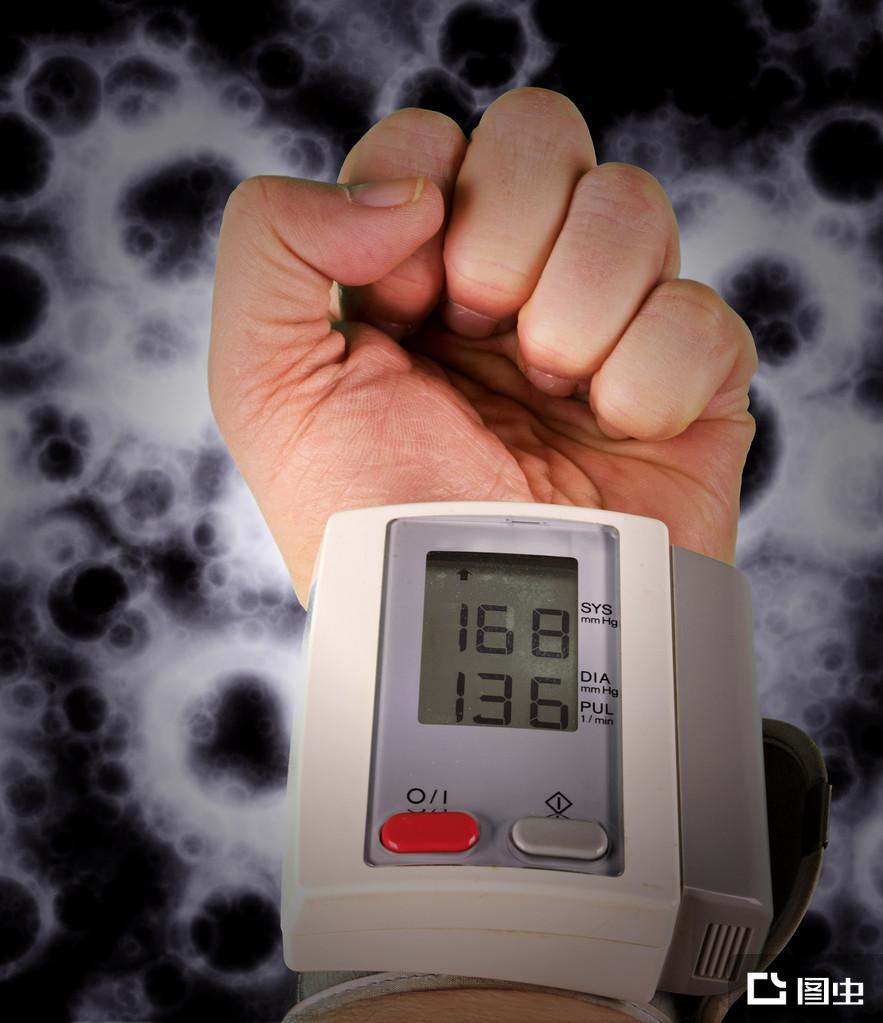

高血压(英文:Hypertension)是指在静息状态以收缩压和(或)舒张压持续升高(收缩压≥140mmHg,舒张压≥90mmHg)为主要临床表现的心血管综合征。

伊扎克·拉宾(希伯来语:יצחק רבין,英语:Yitzhak Rabin,1922年3月1日—1995年11月4日)男,出生于耶路撒冷,以色列政治家、军事家。诺贝尔和平奖获得者,以色列总理。

《科幻世界》(英文名:Sci-Fi World,缩写SFW)是科幻世界杂志社出版的科幻类杂志。创刊于1979年,前身是《奇谈》和《科学文艺》,是中国乃至世界发行量最大的科幻小说杂志,曾获得“世界科幻协会最佳期刊奖”、“中国国家期刊奖提名奖”,并入选“中国百种重点社科期刊”、“双奖期刊”,曾承办过1991年世界科幻协会年会,是中国科幻期刊中一面历久弥新的金牌。杨潇,阿来,秦莉曾先后任杂志社社长,其中阿来任社长期间曾以《尘埃落定》获茅盾文学奖。

尚可名片

这家伙太懒了,什么都没写!

作者