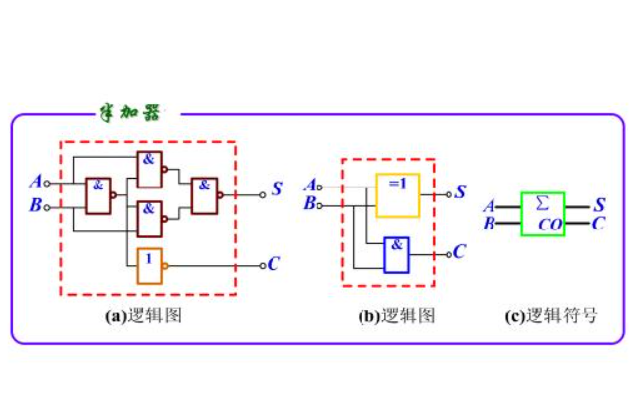

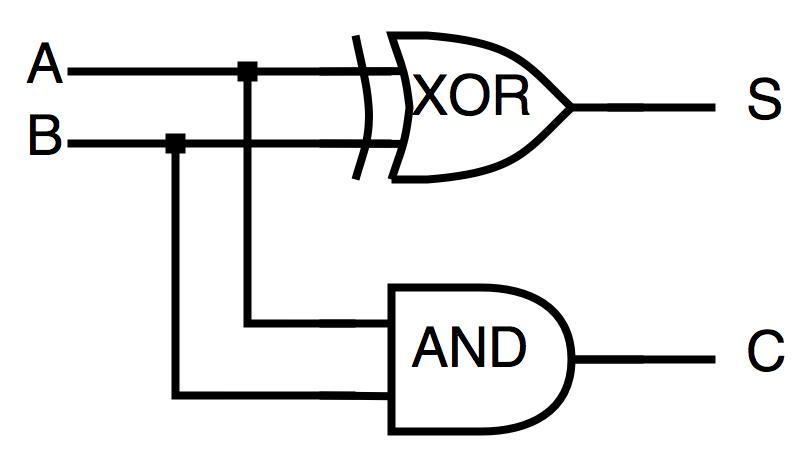

半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。是实现两个一位二进制数的加法运算电路。

精选百科

本文由作者推荐

半加器相关的文章

郭靖,是金庸武侠小说《射雕英雄传》男主角和《神雕侠侣》中的重要角色,《倚天屠龙记》中也曾引述其相关事迹,他是贯通"射雕三部曲"的关键人物之一。融合“降龙十八掌”、“九阴真经”和“左右互搏”三大盖世武功为一体,遂翩然翱翔,武林尊为“天下第一侠士”,黑白二道俯首称臣,号令武林群雄,率领群雄守护着南宋襄阳

玉山铁二(1980年4月7日出生于日本京都府城阳市)是一位日本影视男演员。他毕业于京都府立西城阳高中,并于1999年通过出演个人首部电视剧《麻辣女教师》正式进入演艺圈。2001年,他参演了特摄剧《百兽战队牙吠联者》。2004年,玉山铁二首次担任主演,出演运动电影《功夫棒球》,在片中饰演不屈斗志。20

乌鲁木齐,维吾尔语:“ئۈرۈمچىشەھىرى”,简称乌市,旧称迪化,是中华人民共和国新疆维吾尔自治区辖地级市,首府城市,,位于新疆中北部。截至2022年末,乌鲁木齐市域面积13788平方千米,下辖7个市辖区、1个县,常住人口408.24万人。

章和是东汉章帝刘炟的第三个年号,也是他的最后一个年号,共计18个月。该年号在历史上被用作几个政权的年号。据《资治通鉴》记载,元和四年七月廿七壬戌(87年9月12日),章和正式改元。在章和二年二月,汉和帝即位时沿用该年号,但次年正月初一(89年1月30日)改元永元。

尚可名片

这家伙太懒了,什么都没写!

作者